Product Main Title:

LS028I37-M-V1: 2.8-Inch IPS TFT LCD Module, 240x320 Resolution, 262K Colors, Multi-Interface (Parallel & Serial)

Product Subtitle / Keywords:

2.8 Inch Display, QVGA 240x320 Resolution, Transmissive a-Si IPS TFT, 8080 Parallel & SPI Serial Interfaces, COG+FPC+B/L, 262K Colors, Wide Viewing Angle, 4-Chip White LED Parallel Backlight, ST7789P3 Driver

Comprehensive Technical Specification & Application Guide

1. Executive Summary & Product Positioning

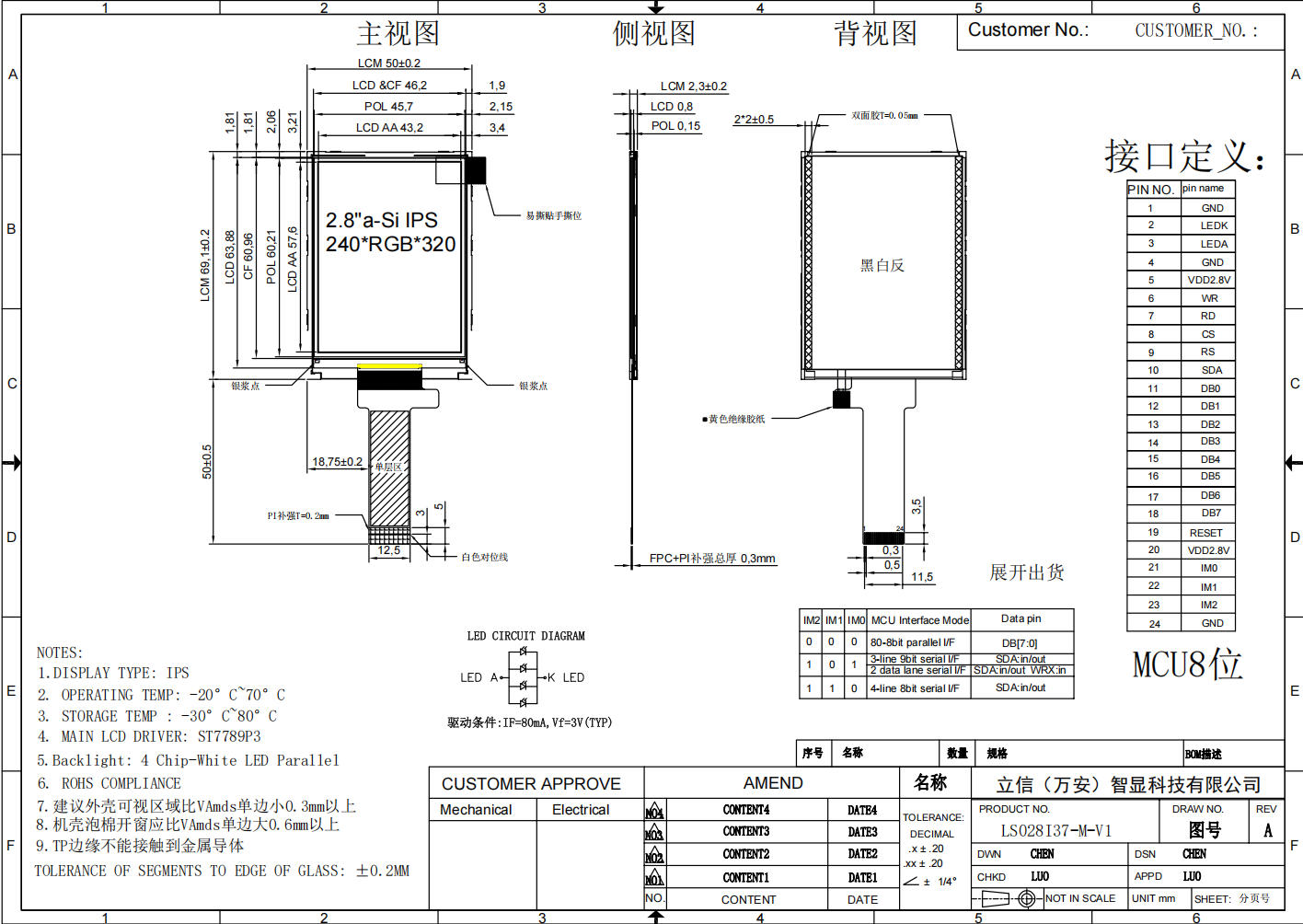

The LS028I37-M-V1, developed by LESSON (Wan'an) Zhixian Technology Co., Ltd., is a 2.8-inch transmissive amorphous Silicon TFT-LCD module featuring IPS (In-Plane Switching) technology for wide viewing angles. This product specification book (Revision 1.0) is the definitive technical document, detailing its structural composition (COG+FPC+B/L), mechanical dimensions, absolute maximum ratings, detailed electrical characteristics, multi-interface (8080 parallel and 3-/4-line serial) timing, and comprehensive electro-optical performance. It delivers a QVGA resolution of 240(RGB)×320 with 262K-color display capability, driven by the ST7789P3 controller. The document provides a complete set of technical indicators and critical assembly guidelines. The unequivocal recommendation for manufacturers and users is to strictly adhere to this specification for design, inspection, and use to ensure module performance, reliability, and optimal display effect in final assembly.

2. Detailed Product Overview & Architecture

- Core Technology: Transmissive-type a-Si TFT-LCD (amorphous silicon thin film transistor liquid crystal display).

- Display Characteristics: Capable of displaying up to 262 thousand colors.

- Module Construction: COG (Chip-On-Glass) + FPC (Flexible Printed Circuit) + B/L (Backlight Unit). Composed of a TFT-LCD panel, a driver circuit, and a backlight unit.

- Interfaces: Configurable via IM[2:0] pins to support:

- 8080-series MCU Parallel Interface (8-bit)

- 3-line Serial Interface

- 4-line Serial Interface (SPI)

- Viewing Direction: Free (IPS).

- Drive IC: ST7789P3.

- Backlight: 4 Chip-White LEDs in parallel.

- Environmental Compliance: ROHS Compliant.

- Approval Status: Approved Product Specification only.

3. Exhaustive Technical Specifications

3.1 Mechanical & Physical Specifications

| Item | Specification | Unit |

|---|---|---|

| Module size (H×V×D) | 50.0 × 69.1 × 2.3 | mm |

| Active area (H×V) | 43.2 × 57.6 | mm |

| Number of dots / Resolution | 240(RGB) × 320 | pixel |

| Panel Size (Diagonal) | 2.8 | inch |

Critical Mechanical & Assembly Notes (from document):

- Backlight: 4 Chip-White LED Parallel.

- ROHS Compliance: Yes.

- Bezel Opening Design: It is strongly recommended that the housing's visible area be at least 0.3mm smaller per side than the module's active area (AA/VAMds).

- Foam Gasket Cutout Design: The cutout in the chassis foam gasket should be at least 0.6mm larger per side than the module's viewing area (VA/VAMds).

- TP/Conductor Isolation: The Touch Panel (TP) edges must not come into contact with any metal conductors.

- Glass Segment to Edge Tolerance: ±0.2 mm.

3.2 Electrical & Interface Specifications

3.2.1 Absolute Maximum Ratings

| Item | Symbol | Min | Max | Unit | Remark |

|---|---|---|---|---|---|

| Supply voltage (Main) | VCC | -0.3 | 4.6 | V | Note1, Note2 |

| I/O Supply voltage | IOVCC | -0.3 | 4.0 | V | Note1, Note2 |

| Operating temperature | TOPR | -20 | 70 | °C | Note1, Note2 |

| Storage temperature | TSTR | -30 | 80 | °C | Note1, Note2 |

Notes (interpreted): Stress beyond these ratings may cause permanent damage; functional operation is not implied.

3.2.2 Electrical Characteristics (DC - Recommended Operating Conditions)

| Item | Symbol | Min | Typ | Max | Unit | Remark |

|---|---|---|---|---|---|---|

| Supply voltage (Main) | VCC | 2.4 | 2.8 | 3.3 | V | Note1 |

| I/O Supply voltage | IOVCC | 1.65 | 1.8 | 3.3 | V | Note1 |

| Input Voltage (Low level) | VIL | 0 | -- | 0.3 * IOVCC | V | Note1 |

| Input Voltage (High level) | VIH | 0.7 * IOVCC | -- | IOVCC | V | Note1 |

3.2.3 Pin Description (21-pin FPC)

| PIN NO. | Symbol | I/O | Description |

|---|---|---|---|

| 1 | GND | P | Ground |

| 2 | LEDK | P | Power for LED backlight cathode |

| 3 | LEDA | P | Power for LED backlight anode |

| 4 | GND | P | Ground |

| 5 | VDD2.8V | P | Main Power Supply (2.8V) |

| 6 | WR | I | Write enable in MCU parallel interface. In 4-line serial, acts as data/command select. If unused, tie to DGND. |

| 7 | RD | I | Read enable in 8080 MCU parallel interface. If unused, tie to VDDI or DGND. |

| 8 | CS | I | Chip selection pin (Low active). |

| 9 | RS | I | Data/Command select in parallel interface. In serial mode, acts as serial clock (SCL). If unused, tie to DGND. |

| 10 | SDA | I/O | SPI interface input/output pin. |

| 11 | D0 | I | Interface data bus bit 0. If unused, tie to DGND. |

| 12 | D1 | I | Interface data bus bit 1. If unused, tie to DGND. |

| 13 | D2 | I | Interface data bus bit 2. If unused, tie to DGND. |

| 14 | D3 | I | Interface data bus bit 3. If unused, tie to DGND. |

| 15 | D4 | I | Interface data bus bit 4. If unused, tie to DGND. |

| 16 | D5 | I | Interface data bus bit 5. If unused, tie to DGND. |

| 17 | D6 | I | Interface data bus bit 6. If unused, tie to DGND. |

| 18 | D7 | I | Interface data bus bit 7. If unused, tie to DGND. |

| 19 | RESET | I | Reset signal. Must be applied to properly initialize the chip. |

| 20 | VDD2.8V | P | Main Power Supply (2.8V) |

| 21 | IM0 | I | Interface Mode selection bit 0 (See IM[2:0] table). |

Interface Mode Selection (IM2, IM1, IM0 Pins):

| IM2 | IM1 | IM0 | MCU Interface Mode |

|---|---|---|---|

| 0 | 0 | 0 | 8-Bit parallel (8080) |

| 0 | 0 | 1 | 8-Bit serial (3-line?) |

| 0 | 1 | 0 | 3-line serial |

| 0 | 1 | 1 | 4-line serial |

| 1 | 0 | 0 | 4-line serial (data input/output) |

| ... | ... | ... | ... (Other combinations likely defined) |

(Note: The full table from the schematic suggests multiple 4-line serial modes. The exact configuration is set by these pins.)

3.2.4 Interface Timing Characteristics

General Conditions: VDDI=1.65 to 3.3V, VDD=2.4 to 3.3V, AGND=DGND=0V, Ta=25°C. Input signal rise/fall time (Tr, Tf) ≤ 15 ns.

A. 8080 Parallel Interface Timing (8-bit bus):

All parameters (Address setup/hold, Chip select timings, Write/Read cycle times, Data setup/hold) are listed as "TBD" (To Be Determined) in the provided document. Final production specs contain concrete values.

B. 3-Line Serial Interface Timing:

Key parameters include SCL "L"/"H" pulse width (Write/Read), data setup/hold time (T_SDS, T_SDH), and access time (T_ACC). All values are listed as "TBD".

Note: A 500 nsec delay is required between the read command and the first read clock in serial interface read sequences.

C. 4-Line Serial Interface Timing:

Key parameters include Chip select setup/hold times (T_CSS, T_CSH), serial clock cycle and pulse widths for Write/Read (T_SCYCW, T_SHW, T_SLW, T_SCYCR, T_SHR, T_SLR), D/CX setup/hold (T_DCS, T_DCH), data setup/hold (T_SDS, T_SDH), and access time (T_ACC). All values are listed as "TBD".

3.2.5 Reset Timing

| Related Pins | Symbol | Parameter | MIN | MAX | Unit | Notes |

|---|---|---|---|---|---|---|

| RESX | T_RW | Reset pulse duration | TBD | - | µs | Must be >9µs to trigger reset. |

| RESX | T_RT | Reset cancel time | - | TBD | ms | Includes time to load settings from NVM. |

Critical Reset Notes:

- Spike Rejection: A reset pulse shorter than 5µs is rejected; between 5µs and 9µs may start a reset; longer than 9µs causes a reset.

- Initialization: During reset, the display blanks and returns to the hardware default condition.

- Setting Load: If a valid reset cancel time (T_RT) occurs within 5ms after RESX rises, initial settings (ID, VCOM, etc.) are loaded from non-volatile memory.

3.2.6 Backlight Unit

- Configuration: 4 Chip-White LEDs in parallel.

- Drive Condition (Typical): Forward Current (I_F) = 80 mA; Forward Voltage (V_f) = 3.0 V.

3.3 Optical & Electro-Optical Characteristics

| Item | Symbol | Condition | Min. | Typ. | Max. | Unit | Remark |

|---|---|---|---|---|---|---|---|

| Response Time | Tr + Tf | θx = θy | -- | -- | 35 | ms | Note 1 |

| Contrast Ratio | CR | θx = θy | 1000 | 1500 | -- | -- | Note 2 |

| Transmittance | T% | θx = θy | 4.5 | 4.8 | -- | % | |

| Color Chromaticity (White) | W x | θx = θy | -- | 0.301 | -- | -- | CIE1931 |

| Color Chromaticity (White) | W y | θx = θy | -- | 0.320 | -- | -- | CIE1931 |

| Viewing Angle (CR>10) | θT, θB, θL, θR | -- | -- | 85 | -- | Deg. | Note 3 |

Notes (from document):

- Response Time: Defined as the LCD optical switching time between "White" and "Black" states. Rise time (Tr) is 10% to 90% change; Fall time (Tf) is 90% to 10% change.

- Contrast Ratio (CR): Measured at panel center.

- Viewing Angle: Measured at the center point using a luminance meter (e.g., BM-5A). Angles are defined relative to the 12 o'clock direction (0°).

4. Application Guidelines & Critical Notes

- Intended Use: Versatile embedded systems, industrial controls, consumer devices, portable instruments—applications requiring a standard 2.8-inch color display with flexibility to choose between high-speed parallel or simpler serial interfaces.

- Critical Design Considerations:

- Interface Selection: Configure the IM[2:0] pins according to the desired interface mode before power-up. This determines the function of key pins like WR, RD, RS, and SDA.

- Mechanical Integration: Strictly follow the housing design rules: Bezel opening > AA - 0.3mm/side; Foam cutout < VA + 0.6mm/side. This prevents pressure-induced Mura (cloudiness) and ensures a clean visual border.

- Power Supply: Provide stable VDD2.8V (2.4-3.3V) and IOVCC (1.65-3.3V). Proper decoupling is essential.

- Backlight Drive: The backlight uses 4 LEDs in parallel. Design a constant-current driver capable of sourcing 80mA at approximately 3V. Do not connect LEDA directly to a voltage source without current limiting.

- Reset Circuit: Ensure the RESET pin receives a low pulse exceeding 9µs during initialization for a guaranteed reset. Adhere to the timing notes regarding cancellation.

- Unused Pins: The pin description specifies grounding recommendations for unused interface pins (e.g., WR, RD, D0-D7 if using serial mode). Follow these to ensure stable operation.

- Temperature Limits: Operate within -20°C to +70°C and store within -30°C to +80°C.

- Handling & Compliance: The module is ROHS compliant. Handle with care to avoid damaging the FPC or glass. Observe standard ESD precautions during assembly.

5. Conclusion & Design-In Support

The LS028I37-M-V1 specification details a highly flexible 2.8-inch IPS display module with multi-interface support. Its key strengths are the wide 85-degree viewing angles inherent to IPS, the choice of 8080 parallel or SPI serial interfaces configurable by hardware pins, and clear, critical mechanical assembly guidelines to achieve optimal display quality in the end product. The main design focus should be on correctly configuring the interface mode, precisely designing the mechanical housing (following the explicit guidelines), providing stable dual power supplies, and implementing a suitable 80mA constant-current LED driver. While the AC timing parameters are listed as TBD in this revision, the core electrical, optical, and functional specifications provide a solid foundation for integrating this versatile module into a wide range of embedded display applications.

Document Prepared Based On: LS028I37-M-V1(SPEC).pdf (Revision 1.0, Published/Uploaded 2026-04-25)